# WINSTAR Display

# **OLED SPECIFICATION**

Model No:

## WEN025664A-CTP

## **General Specification**

| Item             | Dimension          | Unit |

|------------------|--------------------|------|

| Dot Matrix       | 256 x 64 Dots      | _    |

| Module dimension | 85.0 x 39.8 x 7.83 | mm   |

| Active Area      | 69.1 x 17.26       | mm   |

| Pixel Size       | 0.248 x 0.248      | mm   |

| Pixel Pitch      | 0.27 x 0.27        | mm • |

| Display Mode     | Passive Matrix     |      |

| Display Color    | Monochrome         |      |

| Drive Duty       | 1/64 Duty          |      |

| OLED IC          | SSD1322 (COF)      |      |

| OLED Interface   | 6800, 8080, SPI    |      |

| Size             | 2.8 inch           |      |

| CTP IC        | FT6336U      |

|---------------|--------------|

| Detect Point  | 1            |

| CTP Interface | I2C          |

| Surface       | Normal Glare |

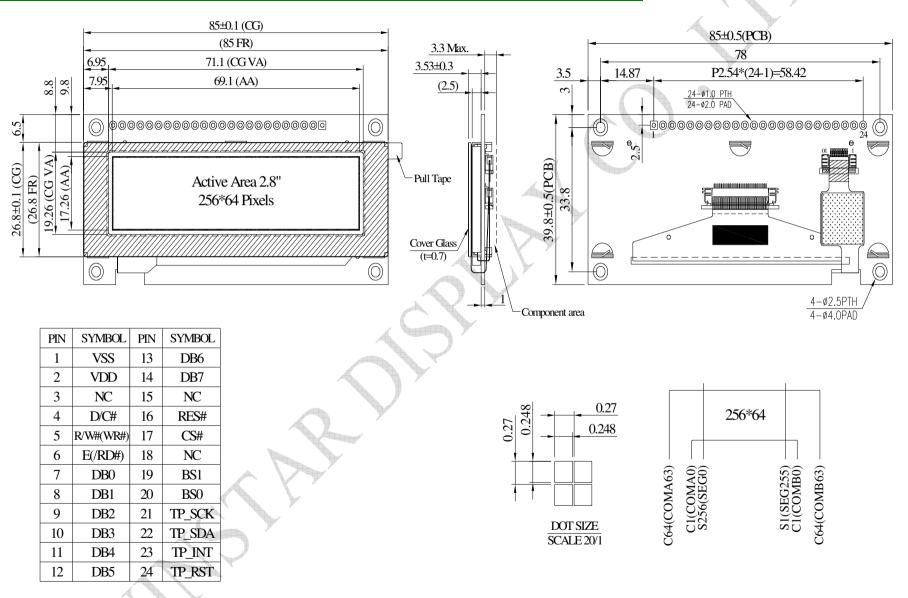

#### **Contour Drawing & Block Diagram**

The non-specified tolerance of dimension is  $\pm 0.3$  mm.

**WINSTAR**

## **Interface Pin Function**

| Pin<br>Number | Symbol                                               | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | VSS                                                  | Р   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2             | VDD                                                  | Р   | <b>Power Supply for Core Logic Circuit</b><br>Power supply pin for core logic operation. A capacitor is required to<br>connect between this pin and VSS                                                                                                                                                                                                                                                                                                                                                                     |

| 3             | N.C.                                                 | Р   | <b>Reserved Pin</b><br>The N.C. pin between function pins are reserved for compatible and<br>flexible design.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4             | D/C#                                                 | I   | Data/Command Control<br>This pin is Data/Command control pin connecting to the MCU.<br>When the pin is pulled HIGH, the content at D[7:0] will be interpreted as<br>data.<br>When the pin is pulled LOW, the content at D[7:0] will be interpreted as<br>command.                                                                                                                                                                                                                                                           |

| 5             | R/W#<br>(WR#)                                        | I   | <b>Read/Write Select or Write</b><br>This pin is MCU interface input. When interfacing to a 68XX-series<br>microprocessor, this pin will be used as Read/Write (R/W#) selection<br>input. Pull this pin to "High" for read mode and pull it to "Low" for write<br>mode.<br>When 80XX interface mode is selected, this pin will be the Write (WR#)<br>input. Data write operation is initiated when this pin is pulled low and the<br>CS# is pulled low.<br>When serial mode is selected, this pin must be connected to VSS. |

| 6             | E/RD#                                                | K   | Read/Write Enable or Read<br>This pin is MCU interface input.<br>When interfacing to a 68XX-series microprocessor, this pin will be used<br>as the Enable (E) signal. Read/write operation is initiated when this pin<br>is pulled high and the CS# is pulled low.<br>When connecting to an 80XX-microprocessor, this pin receives the Read<br>(RD#) signal. Data read operation is initiated when this pin is pulled low<br>and CS# is pulled low.<br>When serial mode is selected, this pin must be connected to VSS.     |

| 7-14          | DB0<br>DB1<br>DB2<br>DB3<br>DB4<br>DB5<br>DB6<br>DB7 | I/O | Host Data Input/Output Bus<br>These pins are 8-bit bi-directional data bus to be connected to the<br>microprocessor's data bus.<br>When serial mode is selected, D1 will be the serial data input SDIN and<br>D0 will be the serial clock input SCLK.                                                                                                                                                                                                                                                                       |

| 15            | NC                                                   | Р   | <b>Reserved Pin</b><br>The N.C. pin between function pins are reserved for compatible and<br>flexible design.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16 | RES#   | Ι | This pin is reset signal input.<br>When the pin is pulled LOW, initialization of the chip is executed.<br>Keep this pin pull HIGH during normal operation.                     |  |  |  |  |

|----|--------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 17 | CS#    | Ι | <b>Data/Command Control</b><br>This pin is the chip select input connecting to the MCU. The chip is<br>enabled for MCU communication only when CS# is pulled LOW.              |  |  |  |  |

| 18 | NC     | Р | <b>Reserved Pin</b><br>The N.C. pin between function pins are reserved for compatible and flexible design.                                                                     |  |  |  |  |

| 19 | BS1    |   | Communicating Protocol Select                                                                                                                                                  |  |  |  |  |

| 20 | BS0    | Ι | Bs[1:0] Bus Interface Selection   00 4 line SPI   01 3 line SPI   10 8-bit 8080 parallel   11 8-bit 6800 parallel   Note (1) 0 is connected to VSS   (2) 1 is connected to VDD |  |  |  |  |

| 21 | TP_SCK | Ι | I2C clock input                                                                                                                                                                |  |  |  |  |

| 22 | TP_SDA | Ι | I2C data input and output                                                                                                                                                      |  |  |  |  |

| 23 | TP_INT | Ι | External interrupt to the host                                                                                                                                                 |  |  |  |  |

| 24 | TP_RST | Ι | External Reset, Low is active                                                                                                                                                  |  |  |  |  |

### **Absolute Maximum Ratings**

#### **Absolute Maximum Ratings**

| Parameter                  | Symbol | Min  | Мах | Unit |

|----------------------------|--------|------|-----|------|

| Supply Voltage for Display | VDD    | -0.3 | 4   | V    |

| Operating Temperature      | TOP    | -20  | 70  | °C   |

| Storage Temperature        | TSTG   | -30  | 80  | °C   |

ຯ

#### **Electrical Characteristics**

#### **DC Electrical Characteristics**

| Item                                 | Symbol | Condition | Min     | Тур | Max     | Unit |

|--------------------------------------|--------|-----------|---------|-----|---------|------|

| Supply Voltage for Logic             | VDD    |           | 2.8     | 3.0 | 3.3     | V    |

| High Level Input                     | VIH    | NY Y      | 0.8×VDD | —   | VDD     | V    |

| Low Level Input                      | VIL    | ) –       | 0       | —   | 0.2×VDD | V    |

| High Level Output                    | VOH    | _         | 0.9×VDD | —   | VDD     | V    |

| Low Level Output                     | VOL    | _         | 0       | _   | 0.1×VDD | V    |

| 50% Check Board<br>operating Current | IDD    | VDD =3V   | _       | 125 | 250     | mA   |